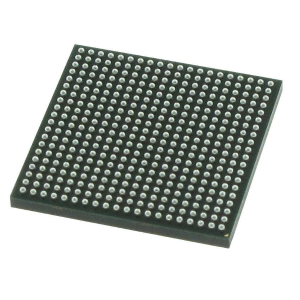

LCMXO1200C-3TN144I FPGA – programovateľné hradlové pole, 1200 LUT, 113 IO, 1,8/2,5/3,3V -3 rýchlosti I

♠ Popis produktu

| Atribút produktu | Hodnota atribútu |

| Výrobca: | Mriežka |

| Kategória produktu: | FPGA - programovateľné hradlové pole |

| RoHS: | Detaily |

| Séria: | LCMXO1200C |

| Počet logických prvkov: | 1200 LE |

| Počet I/O: | 113 V/V |

| Napájacie napätie - Min: | 1,71 V |

| Napájacie napätie - Max.: | 3,465 V |

| Minimálna prevádzková teplota: | - 40 °C |

| Maximálna prevádzková teplota: | + 100 °C |

| Rýchlosť prenosu dát: | - |

| Počet vysielačov a prijímačov: | - |

| Štýl montáže: | SMD/SMT |

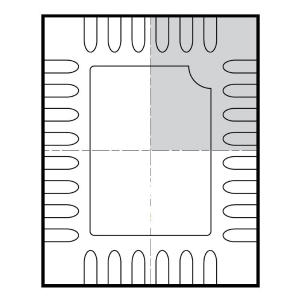

| Balenie/puzdro: | TQFP-144 |

| Balenie: | Zásobník |

| Značka: | Mriežka |

| Distribuovaná RAM: | 6,4 kbit/s |

| Vstavaná bloková RAM - EBR: | 9,2 kbit/s |

| Výška: | 1,4 mm |

| Dĺžka: | 20 mm |

| Maximálna prevádzková frekvencia: | 500 MHz |

| Citlivé na vlhkosť: | Áno |

| Počet blokov logického poľa - LAB: | 150 LABORATÓRIÍ |

| Prevádzkový napájací prúd: | 21 mA |

| Prevádzkové napájacie napätie: | 1,8 V/2,5 V/3,3 V |

| Typ produktu: | FPGA - programovateľné hradlové pole |

| Množstvo v balení z výroby: | 60 |

| Podkategória: | Programovateľné logické integrované obvody |

| Celková pamäť: | 15,6 kbit/s |

| Šírka: | 20 mm |

| Hmotnosť jednotky: | 1,319 g |

Nevolatilný, nekonečne rekonfigurovateľný

• Okamžité zapnutie – zapne sa v priebehu mikrosekúnd

• Jeden čip, nevyžaduje sa žiadna externá konfiguračná pamäť

• Vynikajúca bezpečnosť návrhu, žiadny bitový prúd, ktorý by sa dal zachytiť

• Prekonfigurujte logiku založenú na SRAM v milisekundách

• SRAM a energeticky nezávislá pamäť programovateľné cez JTAG port

• Podporuje programovanie energeticky nezávislej pamäte na pozadí

Režim spánku

• Umožňuje až 100-násobné zníženie statického prúdu

Rekonfigurácia TransFR™ (TFR)

• Aktualizácia logiky v teréne počas prevádzky systému

Vysoká hustota vstupov/výstupov k logickým parametrom

• 256 až 2280 LUT4

• 73 až 271 I/O s rozsiahlymi možnosťami puzdra

• Podporovaná migrácia hustoty

• Balenie bez olova/v súlade s RoHS

Vstavaná a distribuovaná pamäť

• Vstavaná bloková RAM sysMEM™ s kapacitou až 27,6 kbitov

• Distribuovaná RAM s kapacitou až 7,7 kbitov

• Vyhradená riadiaca logika FIFO

Flexibilná I/O vyrovnávacia pamäť

• Programovateľná vyrovnávacia pamäť sysIO™ podporuje širokú škálu rozhraní:

– LVCMOS 3,3/2,5/1,8/1,5/1,2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

PLL obvody sysCLOCK™

• Až dva analógové PLL obvody na zariadenie

• Násobenie, delenie a fázový posun hodín

Podpora na úrovni systému

• Štandard IEEE 1149.1 Boundary Scan

• Vstavaný oscilátor

• Zariadenia pracujú s napájaním 3,3 V, 2,5 V, 1,8 V alebo 1,2 V

• Programovanie v systéme kompatibilné s IEEE 1532